# Using the TMS370 SPI and SCI Modules

Kevin C. Self

Microcontroller Applications Engineering

Semiconductor Group

Texas Instruments Incorporated

Contributions by Paul Krause, Mark Palmer, and Al Lovrich

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to or to discontinue any semiconductor product or service identified in this publication without notice. TI advises its customers to obtain the latest version of the relevant information to verify, before placing orders, that the information being relied upon is current.

TI warrants performance of its semiconductor products to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed.

TI assumes no liability for TI applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

# **Contents**

| Sect                                                                                   | tion                                                                                                                                                                                                                                                                                                                                                                                                    | Page                                                                                                 |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| 1                                                                                      | Introduction                                                                                                                                                                                                                                                                                                                                                                                            | 1-1                                                                                                  |

| 2<br>2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.3<br>2.3.1<br>2.3.2<br>2.4<br>2.5<br>2.6<br>2.7 | Module Description: Serial Peripheral Interface (SPI) The SPI - How It Works SPI Operating Modes The Master Mode The Slave Mode Configuring the SPI SPI Data Format - Transmitting and Receiving The SPICLK and Data Transfer Rate Controlling the SPI through Interrupts and Flag Checking The TALK Bit and Multiprocessor Communications Considerations When Using the SPI Data Integrity and the SPI | 2-3<br>2-3<br>2-3<br>2-4<br>2-4<br>2-5<br>2-6<br>2-7                                                 |

| 3.1<br>3.2<br>3.3<br>3.4                                                               | SPI Module Software Examples  Master SPI Configuration                                                                                                                                                                                                                                                                                                                                                  | . 3-3<br>. 3-4                                                                                       |

| 4.1<br>4.1.1<br>4.2<br>4.2.1<br>4.3<br>4.3.1                                           | SPI Module Specific Applications Vacuum Fluorescent Display Driver Use SPI to Transmit Data to Serial Shift Register Bootstrap Loader Reprogram Data or Program Memory through SPI Port DSP Controller Interface TMS370SPI to TMS320C25 DSP                                                                                                                                                             | . 4-2<br>. 4-8<br>. 4-8<br>. 4-9                                                                     |

| <b>5</b> 5.1 5.2 5.3 5.4 5.5 5.6 5.7 5.8 5.9 5.9.2 5.9.3 5.10 5.10.1                   | Transmitting                                                                                                                                                                                                                                                                                                                                                                                            | . 5-3<br>. 5-4<br>. 5-5<br>. 5-6<br>. 5-7<br>. 5-9<br>. 5-11<br>. 5-12<br>. 5-13<br>. 5-13<br>. 5-14 |

| A<br>B<br>C<br>D<br>E                        | SPI Control Registers SCI Control Registers TMS0170 Specifications Glossary References                                                                              | A-1<br>B-1<br>C-1<br>D-1<br>F-1      |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

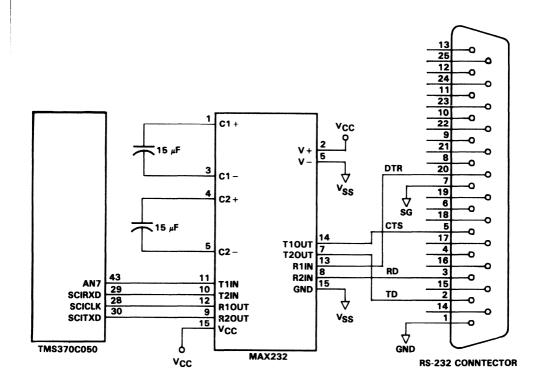

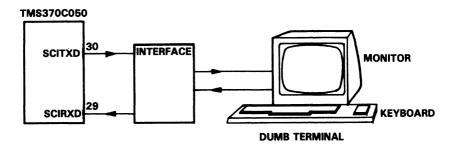

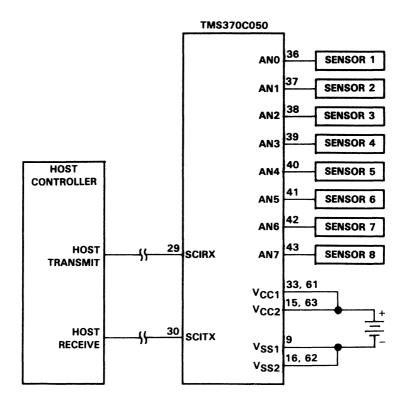

| 7.1<br>7.1.1<br>7.2<br>7.2.1<br>7.3<br>7.3.1 | SCI Module Specific Applications RS-232-C Interface                                                                                                                 | <b>7-1</b> 7-2 7-2 7-6 7-6 7-11 7-11 |

| 6.1<br>6.2<br>6.3<br>6.4                     | SCI Module Software Examples  SLEEP Bit - Multiprocessing Control  System Controller Configuration  Nine-Bit Data Protocol  HALT Mode Wakeup Using the SCI Receiver | 6-1<br>6-2<br>6-3<br>6-4<br>6-5      |

| 5.11<br>5.12                                 | Detecting Transmission Errors                                                                                                                                       |                                      |

# Illustrations

| Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Page                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

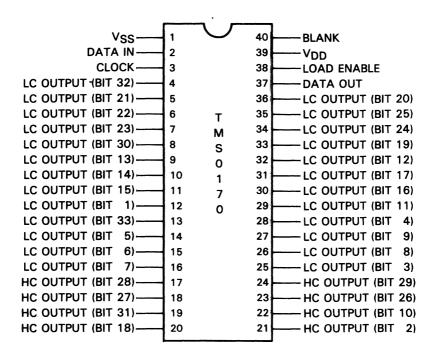

| 2-1 SPI Block Diagram 2-2 SPI Master/Slave Connection 4-1 Vacuum Flourescent Interface Example 4-2 Flowchart of Bootstrap Loader Interrupt Service Routine 4-3 TMS370C010 - TMS320C25 Interface Example 4-4 Continuous Mode No Frame Synchronization Pulse 5-1 SCI Block Diagram 5-2 SCI Data Frame Formats 5-3 Asynchronous Communication Format 5-4 Isosynchronous Communication Format 5-5 Receiver Operation Flowchart 5-6 Transmitter Operation Flowchart 7-1 TMS370C050 - RS-232-C Interface Example 7-2 Terminal Interface Example 7-3 Remote Data Acquisition Example A-1 SPI Control Registers B-1 SCI Control Registers C-1 TMS0170 Block Diagram TMS0170 DIP Pin Out | 2-2<br>4-3<br>4-8<br>4-9<br>4-10<br>5-2<br>5-3<br>5-5<br>5-5<br>5-5<br>7-3<br>7-6<br>7-11<br>A-1<br>A-1 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0-4                                                                                                     |

# **Tables**

| Tabl | e .                                                              | Page |

|------|------------------------------------------------------------------|------|

| 2-1  | SPI Character Bit Length                                         | 2-5  |

| 2-2  | SPI Clock Frequency                                              | 2-5  |

| 2-3  | Baud Rates for SPI Bit Rate Values                               | 2-6  |

| 3-1  | Common Equate Table                                              | 3-1  |

| 5-1  | Transmitter Character Bit Length                                 | 5-4  |

| 5-2  | Asynchronous Baud Rate Register Values for Common SCI Baud Rates |      |

| 6-1  | Common Equate Table                                              |      |

# Section 1

# Introduction

The TMS370 family of 8-bit microcontrollers has been designed with special features to facilitate serial communications. Both the TMS370X5X and TMS370CX10 devices incorporate the Serial Peripheral Interface (SPI) module. The TMS370X5X device also contains the Serial Communications Interface (SCI) module. These two modules greatly enhance the ability of the microcontroller to interface to other serial devices and common interfaces such as the industry standard RS-232. External hardware and software overhead are reduced by the flexibility and programmability of the interfaces.

This application report provides examples of hardware interfaces and software routines to illustrate the versatility of the SPI and SCI modules. Common applications of these modules will be discussed, which may be modified to suit the engineer's specific needs. Additional information on the Serial Interfaces may be found in the TMS370 Family Data Manual.

# Section 2

Module Description: Serial Peripheral Interface (SPI)

### 2.1 The SPI - How It Works

The SPI module is a high-speed synchronous serial I/O port that shifts a serial bit stream of variable length and data rate between the device and other peripheral devices. The SPI is especially suited for multiprocessor and external peripheral communications, where the designer needs high-speed synchronous data transfer. The use of the SPI can greatly reduce overhead when connecting several peripherals together by transferring address or status information. The SPI can be used to communicate with other microcontrollers, serial shift registers, or display drivers. In addition, the SPI can be used to load memory (RAM or EEPROM) and allow the device to be reprogrammed insocket.

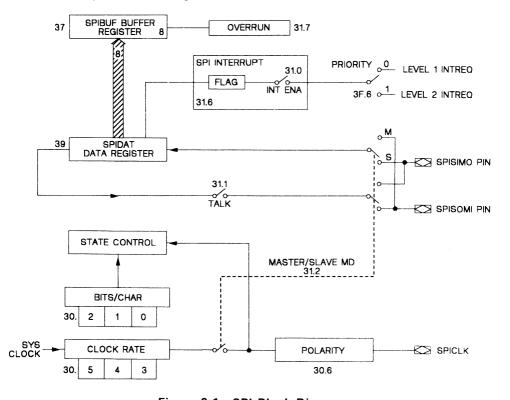

A block diagram of the SPI is shown in Figure 2-1. In its simplest form, the SPI can be thought of as a fast, programmable shift register. Data is shifted in and out of the SPI through the SPIDAT register. Data to be transmitted is written to the SPIDAT register and received data is latched into the SPIBUF register to be read. Data transmission rates and data formatting are controlled by the SPI state logic.

Figure 2-1. SPI Block Diagram

### 2.2 SPI Operating Modes

### 2.2.1 The Master Mode

The SPI operates in one of two modes. The Master mode is used when the SPI controls the data transfer. The Master SPI initiates and controls the data transfer by issuing the SPICLK signal. Writing data to the SPIDAT buffer starts the transfer by starting SPICLK and shifting the data out of the SPIDAT shift register onto the SPISIMO pin. New data are simultaneously gated in on the SPISOMI pin into the SPIDAT buffer.

Since the Master device controls the data transfer by issuing the SPICLK, the other devices must wait for the Master to start the transmission. Even if the Master is only interested in receiving data, it is still necessary to write "dummy" data to the SPIDAT register to initiate the transfer from the slave or external source.

Because of the way data are shifted through the SPIDAT Register, any data value in SPIDAT is always modified after a transmission, even if no new data value has been received into the register. The SPIDAT register will contain indeterminate data because no new data have been received.

### 2.2.2 The Slave Mode

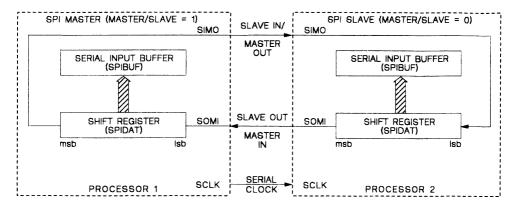

The Slave mode is used when the SPI is controlled by another serial device. In the Slave mode, the SPI is dependent on an external clock source from a Master configured device to control the data transfer. An element of data resident in the SPIDAT buffer is shifted out upon receipt of a clock signal on the SPICLK pin, which in Slave mode becomes an input pin. Simultaneously, any data present on the SPISIMO pin are shifted into the SPIDAT register. The data transmission of a slave can be disabled by clearing the TALK bit. This allows many devices to be tied to the same serial network, but eliminates the possibility of write conflicts. Figure 2-2 illustrates two TMS370 devices in a Master/Slave connection.

Figure 2-2. SPI Master/Slave Connection

### 2.3 Configuring the SPI

Data format, baud rate, interrupt generation, and operating mode are controlled by setting the SPI control registers shown in Appendix A. The SPI should be in an SPI SW RESET condition before changing any of the configuration registers. This freezes the state of the SPI while it is being configured. After setting the SPI parameters, release the reset. Before initiating a data transmission you need to initialize the parameters discussed in the following sections.

# 2.3.1 SPI Data Format - Transmitting and Receiving

Character length is programmable and can be set by the user from 1 to 8 bits. This is done by setting SPICCR bits 0-2 to the appropriate values shown in Table 2-1. If the character length is fewer than 8 bits, it is important to note the following:

- Data must be written to SPIDAT left justified. Data is shifted out of the SPIDAT register MSB first, and if the character is not left justified the data will be corrupted.

- 2) Data is received into SPIDAT right justified. The MSB of the transmitted data is shifted into the LSB of SPIDAT and walked across. For character lengths + 8 bits, there will be extra bits containing information from previous transmissions that must be accounted for

### 2.3.2 The SPICLK and Data Transfer Rate

The rate at which data are transferred out of SPIDAT is programmed by the SPI Bit Rate bits (SPICCR.3-5). The rate can be set from CLKIN/8 to CLKIN/1024 as shown in Table 2-2. The SPICLK rate is only utilized in the Master mode; in Slave mode the SPICLK rate is irrelevant because the clock signal is external. The SPICLK is output anytime a write is made to SPIDAT and the device is in the Master mode. The polarity of the clock bit can be set by the user (SPICCR.6) to latch the data on the rising or falling edge of the clock pulse. When an external clock is being used (Slave mode), the input clock frequency cannot be greater than CLKIN/32 to allow the internal clocks to synchronize.

Table 2-1. SPI Character Bit Length

| Char2 | Char1 | Char0 | Character<br>Length |

|-------|-------|-------|---------------------|

| 0     | • 0   | 0     | 1                   |

| 0     | 0     | 1     | 2                   |

| 0     | 1     | 0     | 3                   |

| 0     | 1     | 1     | 4                   |

| 1     | 0     | 0     | 5                   |

| 1     | 0     | 1     | 6                   |

| 1     | 1     | 0     | 7                   |

| 1     | 1     | 1     | 8                   |

Table 2-2. SPI Clock Frequency

| SPI†<br>Bit<br>Rate2 | SPI†<br>Bit<br>Rate1 | SPI†<br>Bit<br>Rate0 | SPI Clock<br>Frequency |

|----------------------|----------------------|----------------------|------------------------|

| 0                    | 0                    | 0                    | CLKIN/8                |

| 0                    | 0                    | 1                    | CLKIN/16               |

| 0                    | 1                    | 0                    | CLKIN/32               |

| 0                    | 1                    | 1                    | CLKIN/64               |

| 1                    | 0                    | 0                    | CLKIN/128              |

| 1                    | 0                    | 1                    | CLKIN/256              |

| 1                    | 1                    | 0                    | CLKIN/512              |

| 1                    | 1                    | 1                    | CLKIN/1024             |

<sup>†</sup> If the SPI is a network slave, the module receives a clock on the SPICLK pin from the network master; and these bits have no effect on SPICLK. The frequency of the input clock should be no greater than the CLKIN frequency divided by 32.

A table showing the baud rates for common crystal frequencies vs. SPI bit rate values is shown below. See Table 2-3. The values were found using the formula

SPI BAUD RATE = CLKIN /  $(8 \times 2^b)$

where b = bit rate specified in the SPI Control Register (SPICCR.5-3) (range 0-7).

Crystal/Oscillator Frequency (MHz) Divide By 2.00 5.00 10.00 15.00 20.00 2500000 8 250000 625000 1250000 1875000 16 125000 937500 1250000 312500 625000 32 62500 156250 312500 468750 625000 78125 64 31250 156250 234375 312500 128 15625 39062.5 78125 117187. 156250 7812.5 256 19531.2 39062.5 58593.7 78125 512 3906.25 9765.62 19531.2 29296.8 39062.5 1024 1953.12 4882.81 9765.62 14648.4 19531.2

Table 2-3. Baud Rates for SPI Bit Rate Values

# 2.4 Controlling the SPI through Interrupts and Flag Checking

The SPI interrupt logic can generate an interrupt upon receiving or transmitting a complete character as determined by the SPI character length. This provides a convenient and efficient way to handle the reception or transmission of data.

The interrupt can be enabled or disabled using the SPI INT ENA bit (SPICTL.0), and the interrupt priority set with the SPI PRIORITY bit (SPI-PRI.6). Whether or not the SPI interrupt is enabled, the SPI INT flag (SPICTL.6) will be set upon the transmission or reception of a character. The SPI INT flag cannot be cleared as it is Read Only, but it is automatically cleared when SPIBUF is read, the SPI SW RESET Bit is set, or a system reset. Even if a data value is not going to be saved, it is still necessary to do a "dummy" read to clear the SPI INT flag. If the flag is not cleared and the interrupts are enabled then the interrupt routine will be called again as soon as it is completed.

Data transmission is not instantaneous in the SPI. It will be necessary to wait for the SPI to transmit or receive a character before reading from or writing to the SPIDAT register again. There are two ways to do this:

When the SPI has transmitted or received new data the SPI INT routine will be generated if enabled. The character is ready to be read if it was just received, or a new character can be transmitted if desired.  If the program cannot do anything until the new data value is received or transmitted, the SPI INT flag can be continuously polled until it goes high, at which time the character is ready to be read or a new one transmitted.

It is important to use one of the above methods to wait for the data before reading or writing again. Also, if the exact number of cycles is known, the transmission can be timed that way. When doing fast data transfers where the possibility of a data collision exists, polling the RECEIVER OVERRUN flag (SPICTL.7) will indicate if you have lost any data.

### 2.5 The TALK Bit and Multiprocessor Communications

If more than two processors are going to be connected to the same SPI data lines (SPISIMO/SPISOMI), then it will be necessary to limit the conversation to just two processors at a time. This is done through software using the TALK bit (SPICTL.1). When the TALK bit is 0, data transmission is disabled, but not reception. One device, usually (but not necessarily) the Master, sends out an address to the other devices in the network, who have their TALK bits set to 0. Since reception is not affected, all devices receive the transmitted address and compare it against their own address. If it matches, then that device sets its TALK bit and begins transmitting data. When it finishes, the receiving device clears its TALK bit and the network waits for another address. Another scheme for using the TALK bit is to have groups of characters (10 or so) transmitted in a block and have the address be the first character transmitted in a block. This way the address will occur at regular intervals and address checking does not need to be done constantly.

# 2.6 Considerations When Using the SPI

The most important thing to remember when writing SPI service routines is to keep your code short. Received data should be quickly removed from the SPIBUF register to prevent it from being overwritten. If you have to manipulate the data, wait until all the data have been received first. If your code involves long SPI routines there is a possibility that new data will be received before the previous data value has been read from the SPI buffer register. This becomes more and more important as the SPI baud rate increases.

### 2.7 Data Integrity and the SPI

The SPI was designed as a fast, simple interface to serial logic. As a result, it has no direct way to check for transmission errors. There are a number of software methods that can be used to check the integrity of the transmission. Parity checking is one of the most common and can be easily implemented in software for the SPI. Parity checking involves reserving one bit of the character to be used in setting the total number of 1s in a character odd or even. The Design Aids section of the TMS370 Family Data manual contains an example of a parity checking routine.

If you are going to be sending large blocks of data, there are coding methods that allow faster data transfer but still insure data integrity. Block checksums and other encoding methods can be found in most books on digital communications. These methods allow some degree of data integrity without significantly slowing the data transfer rate.

# **Section 3**

# **SPI Module Software Examples**

The following are examples of the various modes of operation and common software routines used in the utilization of the SPI. The SPI Control Registers are..shown in Appendix A. The Register Equate table for the following examples is shown below.

Table 3-1. Common Equate Table

| .equ | P030                         | ;SPI Configuration, Control Register                          |

|------|------------------------------|---------------------------------------------------------------|

| .equ | P031                         | ;SPI Operation Control Register                               |

| .equ | P037                         | ;Serial Input Buffer                                          |

| .equ | P039                         | ;Serial Data Register                                         |

| .equ | PO3D                         | ;SPI Port Control Register 1                                  |

| .equ | PO3E                         | ;SPI Port Control Register 2                                  |

| .equ | PO3F                         | ;SPI Priority Control Register                                |

| -    |                              | · · · · · · · · · · · · · · · · · · ·                         |

|      | .equ<br>.equ<br>.equ<br>.equ | .equ P031<br>.equ P037<br>.equ P039<br>.equ P03D<br>.equ P03E |

### 3.1 Master SPI Configuration

This routine will show how to configure the SPI to operate in the Master mode. Data will be sent to a peripheral device. The value needed for the SPI Bit rate register is computed from the formula:

```

SPI BAUD RATE = CLKIN / (8 \times 2^b)

```

where b is the bit rate from SPICCR.3-5, in the range from 0-7. This is important in applications where it is necessary to fix the real-time frequency of SPICLK, such as interfacing to slow peripheral logic.

The SPI in this example with a CLKIN of 20 MHz is connected to a shift register with a maximum operating frequency of 250 KHz. The bit rate needed is

```

b = log_2 [ CLKIN / (SPI BAUD RATE × 8 ) ]

b = log_2 [ 20 x 10<sup>6</sup> / (250 x 10<sup>3</sup> × 8 ) ] = 3.35 (approximately)

```

Since only integers are allowed, the bit rate should be set to the next highest value, i.e., 4, which is CLKIN / 128. This gives an actual SPI BAUD Rate of 156.25 KHz, which is within the operating range of the shift register. The character size will be 8 bits.

```

SETMASTER

MOV

#OE7h,SPICCR

;SPI Reset, clock active low, /128, 8 bits

; Master Mode, Enable TALK, Disable SPI INT

MOV

#006h,SPICTL

MOV

#002h,SPIPC1

;Set for SPICLK out

MOV

#022h,SPIPC2

;Enable SPISOMI, SPISIMO pins for SPI

MOV

#040h,SPIPRI

;SPI interrupts are low priority

AND

#067h,SPICCR

;Release SPI Reset

;Execute main program here. When ready

; to transmit, call subroutine

CALL

SENDDATA

;Execute subroutine

SENDDATA

VOM

DATAOUT, SPIDAT

; Move data to SPIDAT, initiate transmission

#040h,SPICTL,WAIT ;Loop until transmission complete

WATT

BTJZ

;Dummy read to clear SPI INT flag

MOV

SPIBUF, DUMMY

RTS

;Return to main program

```

## 3.2 Slave SPI Configuration

This routine will show how to use the SPI interrupt to interrupt a program and load two 8-bit characters from the SPI. The program will call the SPI Interrupt upon receipt of an 8-bit character, save it, and wait for one more character. It will then save the values, and return to the main program. The characters will be saved in DATAMSB and DATALSB.

| SETSLAVE        | DINT<br>MOV<br>MOV        | #0E7h,SPICCR<br>#001h,SPICTL                                 | ;Disable Global interrupts.<br>;SPI Reset, clock active low, /128, 8 bits.<br>;Slave mode, TALK disable, SPI INT Enable.                     |

|-----------------|---------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|                 | MOV<br>MOV<br>MOV<br>EINT | #002h,SPIPC1<br>#022h,SPIPC2<br>#040h,SPIPRI<br>#067h,SPICCR | ;Set SPICLK. ;Enable SPISOMI, SPISIMO pins for SPI. ;SPI interrupts are low priority. ;Release SPI RESET. ;Enable global interrupts.         |

|                 |                           |                                                              | ;Insert main part of program here. SPI<br>; INT will fetch characters when first<br>; is detected.                                           |

| SPIINTR<br>WAIT | MOV<br>BTJZ<br>MOV<br>RTI | SPIBUF, DATAMSB<br>#040h, SPICTL, WAIT<br>SPIBUF, DATALSB    | ;Save first character already in buffer.<br>;Wait until second character is received.<br>;Save second character.<br>;Return to main program. |

### 3.3 Dynamic Bit Justification

On occasion it may be necessary to transmit characters of length less than 8 bits. As stated previously, the data need to be left-justified for transmitting from SPIDAT and right-justified when read from SPIBUF. If the SPI is accessing several peripherals with different character lengths, it may be more efficient to have one subroutine justify all the transmitted data.

This routine reads the value of the character length stored in SPICCR.0-2 and left-justifies the data to be transmitted as needed. If the character length is less than 5 bits, the routine swaps nibbles to save time. The value to be transmitted is stored in register DATA.

| LJUSTIFY |      | SPICCR, NUMBITS<br>#OFFh, NUMBITS<br>#007h, NUMBITS<br>#004h, NUMBITS, ROLL<br>DATA | ;Save character length in temp register.<br>;8 - numbits = number of shifts.<br>;clear all bits except character length.<br>;If < 4 shifts needed go to roll routine.<br>;More than 4 shifts, swap is faster. |

|----------|------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | SUB  | #004h,NUMBITS                                                                       | ;Since we swapped, 4 rolls are complete.                                                                                                                                                                      |

|          | JZ   | DONE                                                                                | ;If only 4 rolls needed we are done.                                                                                                                                                                          |

| ROLL     | RL   | DATA                                                                                | ;Rotate one bit left.                                                                                                                                                                                         |

|          | DJNZ | NUMBITS, ROLL                                                                       | ;If not done rotating, continue.                                                                                                                                                                              |

| DONE     | MOV  | DATA, SPIDAT                                                                        | ;Data is now left justified, transmit.                                                                                                                                                                        |

# 3.4 Address Recognition by SPI

In multiprocessor systems using the SPI for communication it is necessary to keep conversations limited to two microprocessors at a time. The TALK bit is used to disable the transmit ability of a TMS370 in Slave mode until it sees its address, MYADDRESS, at which time it will transmit a byte of data. This example shows the SPI interrupt routine which is called when a character is received. If it is the correct address, the TALK bit is set, SPIDAT is loaded, and the TALK bit is cleared once again.

| SPIINTR | MOV<br>CMP<br>JNZ<br>OR<br>MOV | SPIBUF, ADDRESS<br>#MYADDRESS, ADDRESS<br>DONE<br>#002h, SPICTL<br>DATA, SPIDAT | ;Store received address<br>;Is it my address?<br>;If not, ignore transmission.<br>;Set TALK bit.<br>;Load transmit buffer, wait for clock<br>; from "master". |

|---------|--------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TIAW    | BTJZ<br>MOV                    | #040h,SPICTL,WAIT<br>SPIBUF,DUMMMY                                              | ;Wait until character is sent.<br>;Dummy read to clear SPI INT flag                                                                                           |

| DONE    | AND<br>RTI                     | #OFDh,SPICTL                                                                    | ;Clear TALK bit. ;Return from interrupt.                                                                                                                      |

# **Section 4**

# **SPI Module Specific Applications**

### 4.1 Vacuum Fluorescent Display Driver

### 4.1.1 Use SPI to Transmit Data to Serial Shift Register

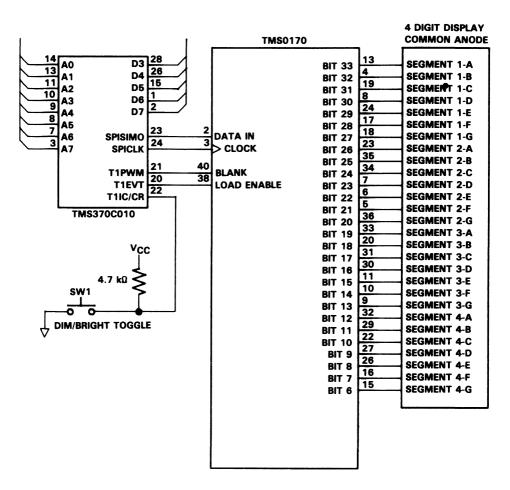

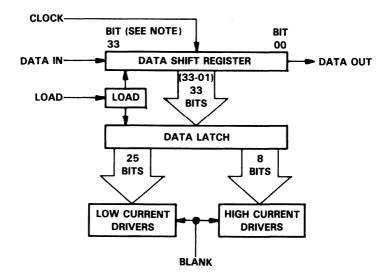

One common and very practical use of an SPI is sending serial data to a display. The use of simple software routines can simplify your design and eliminate expensive external hardware such as decoders. This example interfaces a TMS370C010 microcontroller to a vacuum fluorescent display. The only external logic necessary is one TMS0170 VF Display Driver. This device is a 33-bit shift register/display driver and is especially suited for serial display applications. The design uses only SPI and Timer 1 pins, so the designer does not need to dedicate any more I/O pins to the design. The schematic shown is for a generic serial display application, and it can be easily modified to work with an LED or LCD display.

Figure 4-1. Vacuum Flourescent Interface Example

In this example, the display is pulsed periodically to adjust the intensity and update the display. In addition, the display may be put into a dim mode by toggling the T1 IC/CR pin. The Timer 1 PWM pin is used to control the brightness of the display by pulsing the blanking input of the TMS0170. The data are latched into the TMS0170 by pulsing the T1EVT pin which is configured as an output. When the new data value is to be displayed it is shifted out of the SPI.

The display update routine is controlled by Timer 1 interrupts. The Compare 1 and Compare 2 registers are set to control the refresh rate and intensity, respectively. Because the display is pulsed more frequently than new values are calculated, an interval counter is used to specify when it is time to update the display value. In this example, the following parameters are used:

Refreshes/sec = 100 (Will eliminate flicker in display)

Display updates/sec = 2 CLKIN Freq. = 20 MHz prescale divide = 16 normal display intensity = 90% dim display intensity = 40%

The Timer 1 compare register values are found from the formulas:

Compare 1 value =

$$\frac{\text{CLKIN Freq.}}{4 \times \text{refreshes/sec} \times \text{prescale divide}}$$

Compare 1 value =

$$\frac{20,000,000}{4 \times 100 \times 16} = 3125 \text{ or } 0C35h$$

Compare 2 value = intensity × compare 1 value Compare 2 value (bright) = 0.9 × 3125 = 2812 or 0AFCh Compare 2 value (dim) = 0.4 × 3125 = 1250 or 04E2h

By XORing the bright and dim values together, we get the logical "difference" between the two values. XORing the "difference" with either the bright or dim values will give the other. This is an easy and quick way to toggle the brightness.

DIFFMSB = Compare 2 value (dim) MSB XOR Compare 2 value (bright) MSB DIFFLSB = Compare 2 value (dim) LSB XOR Compare 2 value (bright) LSB

The interval counter value is found from the following formula:

interval = 100 / 2 = 50 or 32h

### The source code for this application is as follows:

```

.title

"Display Driver"

This routine will use the SPI and timer 1 modules to output values to a serial display. The display is updated every 0.5 seconds.

;

;

display intensity is changed by toggling T1IC/CR pin.

SPICCR

.eau

;SPI register assignments.

SPICTL

P031

.equ

SPIDAT

P039

.equ

SPIBUF

P037

.equ

SPIPC1

.equ

PO3D

SPIPC2

.equ

P03E

T1CNTRMSB .equ

P040

;Timer 1 register assignments.

T1CMSBLSB .equ

P041

P042

T1CMSB

.equ

T1CLSB

P043

.equ

T1CCMSB

P044

.equ

T1CCLSB

.equ

P045

T1CTL1

.equ

P049

T1CTL2

PO4A

.equ

T1CTL3

P04B

.equ

T1CTL4

.equ

PO4C

T1PC1

.equ

P04D

T1PC2

.equ

PO4E

T1PRI

PO4F

.equ

Allocate register space for the registers used in the application

routine.

DISPMSB

.equ

R5

;High byte of display value.

DISPLSB

.equ

R6

;Low byte of display value.

ICOUNT

R7

.equ

:Time between display refreshes.

DCOUNT

R8

.equ

DIGITO

.equ

R10

;BCD values of display digits

DIGIT1

.equ

R11

;

DIGIT2

.equ

R12

;

.,

DIGIT3

.equ

R13

;

TEMPMSB

.equ

R14

.equ

TEMPLSB

R15

DUMMY

.equ

R16

Assign values for display intensity, and refresh period.

TIMER

.equ 3125

;100 interrupts/sec @ 20 MHz.

BRIGHT

.equ TIMER*9/10 ; Max intensity = 90 .

.equ BRIGHT ^! (TIMER*4/10); Min intensity = 40 .

DIFF

INTERVAL

.eau 50

.text 07000h

START

DINT

;Disable all interrupts.

SPI Initialization

#0E6h,SPICCR

MOV

; Reset SPI, data out on falling SPICLK,

; 7-bit characters.

MOV

#006h,SPICTL

; Master, Enable TALK, Disable SPI INT.

MOV

;Enable SPICLK out.

;Set SPISIMO out.

#002h,SPIPC1

MOV

#020h,SPIPC2

Set delays for brightness, and value updates

;

#HÍ(TIMER),TÍCMSB

;Load Compare 1 register with delay.

; Time between refreshes (10 mS).

MOV

MOV

#HI(TIMER),T1CLSB

MOV

#HI(BRIGHT),T1CCMSB; Set display to Bright intensity.

MOV

#LO(BRIGHT),T1CCLSB;

MOV

#INTERVAL, ICOUNT

;Temp register for interval counter.

```

```

Timer 1 Initialization

:

;Set T1EVT as general I/O.;Set T1IC/CR to input.;Set T1 interrupts to low priority.

#001h,T1PC1

MOV

#062h,T1PC2

#040h,T1PRI

MOV

MOV

#071h,T1CTL4

;Dual-compare,Disable interrupts.

MOV

;System clock / 16.

#005h,T1CTL1

MOV

MOV

#000h,T1CTL3

:Disable T1 interrupts, clear flags.

#001h,T1CTL2

;Disable Overflow interrupts, Reset T1.

MOV

:

Enable Timer1 & SPI

MOV

#005h;T1CTL3

:Enable T1EDGE INT, Enable T1C1 INT.

#066h,SPICCR

;Release SPI

MOV

#OFOh,B

; Move stack pointer value to B.

MOV

LDSP

;Set stack Pointer.

EINT

;Global interrupt enable.

;Main Loop

MAIN

Place major portion of code here. This part of the program should calculate the value to be displayed, scale it from 0 to 9999, and store the result in DISPMSB and DISPLSB. When Timer 1 counts down

:

the interrupt will be called and the program will jump to DISPLAY.

;

MOV

#??,DISPMSB

; Move sample value into memory.

MOV

#??,DISPLSB

JMP

MAIN

Timerl Interrupt Routine.

This routine pulls the value to be displayed from DISPMSB and

;

DISPLSB, converts it to a packed 4 nibble BCD number and shifts the result out through the SPI. The routine checks to see whether the routine was called by the timer or the TlC1 pin and clears

:

DISPMSB and DISPLSB are temporary registers

the appropriate flag.

and will not contain their original values upon completion of the

interrupt routine.

DISPLAY

BTJZ #080h,T1CTL3,TIMERINT; Was interrupt from T1IC/CR Pin?

T1IC/CR Pin called interrupt, toggle the intensity bright/dim.

:

MOV

#003h,T1CTL1

;Stop timer.

MOV

#001h,T1CTL2

; Reset timer (T1 SW RESET).

#050h,T1PC2

VOM

;Set PWM as general purpose I/O.

;Set T1PWM=1 (command must be repeated).

VOM

#050h,T1PC2

MOV

;Reenable T1PWM.

#060h,T1PC2

MOV

T1CCLSB, TEMPLSB

;Get current display intensity.

T1CCMSB, TEMPMSB

MOV

#LO(DIFF), TEMPLSB

XOR

;Toggle display intensity.

XOR

#HI(DIFF),TEMPMSB

MOV

TEMPMSB, T1CCMSB

;Update display intensity

MOV

TEMPLSB, T1CCLSB

MOV

#005h,T1CTL1

;Restart timer.

;Clear TlIC/CR interrupt flag. ;End of display toggle: wait for update.

AND

#07Fh,T1CTL3

JMP

DONE

TIMERINT

DJNZ

ICOUNT, NOTNOW

; Is it time for new value to be displayed?

; if it is not, do not calc new value.

MOV #INTERVAL.ICOUNT

:Restore interval counter

```

```

Hex to BCD Conversion Routine.

;

DIGIT2

CLR

;Clear result registers.

CLR

DIGITO

;Set loop count.

MOV

#16,R3

LOOP

RLC

DISPLSB

;Shift high bit out.

RLC

DISPMSB

; Carry contains the high bit.

DAC

DIGITO, DIGITO

;Double the number then add high bit.

DAC DIGIT2, DIGIT2

DJNZ R3,LOOP

:Loop until multiplied 16 times.

MOV

DIGITO, DIGIT1

;Save second digit

MOV DIGIT2, DIGIT3

;Save third digit

SWAP

DIGITI

;Swap BCD nibbles

;Swap BCD nibbles

SWAP

DIGIT3

#OFh,DIGITO

AND

;Clear high nibble

:Clear high nibble

AND

#OFh, DIGIT1

AND

#OFh, DIGIT2

;Clear high nibble

AND

#OFh.DIGIT3

;Clear high nibble

Output Display Values.

;

This part actually outputs the BCD values to the display through the SPI. Note that in this example the display is limited to 4 characters, which gives a maximum value of 9999.

:

MOV

#000h,DCOUNT

;Set counter for data address.;Store DCOUNT in temp register.

DCOUNT, B

NEXTCHAR

MOV

MOV

DIGITO(B),A

; Move BCD value of current char into A.

XCHB A

; Move BCD value into B.

MOV

TABLE(B),A

;Look up 7seg value and store in A.

MOV

A, SPIDAT

;Move character byte into SPIDAT register. ;Wait for character to be sent.

WATT1

BTJZ #040h, SPICTL, WAIT1

MOV

SPIBUF, DUMMY

;Dummy read to clear SPI INT flag.

INC

DCOUNT

;Location of next digit register

BTJZ #004h,DCOUNT,NEXTCHAR;If <4 characters sent, then send another.

MOV #005h,T1PC1 ;Toggle T1EVT to latch data.

MOV

;Pull T1EVT low again.

#001h,T1PC1

OR

#001h.T1CTL4

;Re-enable T1IC/CR interrupt here. This

; allows delay between recognition of dim/

; bright toggles to debounce switch.

NOTNOW

#ODFh,T1CTL3

;Clear T1C1 interrupt flag.

AND

DONE

RTT

;Return from interrupt.

Look-up table for converting BCD values to 7-segment display values.

Display BCD Value

TABLE

#07Eh

.byte

.byte

#00Ch

#0B6h

2

The segments are decoded as follows:

.byte

:

#09Eh

3

SEGMENT|gfedcba0

BIT|76543210

.byte

;

#0CCh

.byte

; 5

.byte

#ODAh

.byte

#OFAh

6

;

.byte

#00Eh

#OFEh

.byte

;

#0CEh

.byte

Set up interrupt vector addresses

;

"Vectors",07FF4h

.sect

.word

DISPLAY

;Timer 1 interrupt

.word

START

;All other vectors go to 'START'.

START

.word

.word

START

.word

START

.word START

```

### 4.2 Bootstrap Loader

### 4.2.1 Reprogram Data or Program Memory through SPI Port

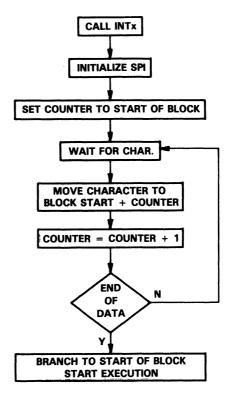

The SPI is very useful as a bootstrap loader for loading program or data information directly into RAM, EPROM, or EEPROM. The TMS370 family SPI and instruction set provide a fast, efficient way of moving serial data directly into memory. With the addition of a small interrupt service routine, the memory loader can become a bootstrap loader to reprogram a device in-socket, in the field. The interrupt routine must do the following:

Figure 4-2. Flowchart of Bootstrap Loader Interrupt Service Routine

The interrupt routine loads the received data into program memory beginning at a specified location. After the data has been loaded in, the Program Counter is set to the beginning of the block and program execution is transferred to the new program. The new program can reconfigure the part as desired, or modify the program or data memory. An example of this is provided in the TMS370 family EEPROM Applications Report.

### 4.3 DSP Controller

### 4.3.1 Interface TMS370 SPI to TMS320C25 DSP

This example shows how the SPI can be used to communicate with other microprocessors. The exact method of communication varies from system to system, but the key parts can be shown to demonstrate how to interface the TMS320C25 and TMS370 serial ports. The TMS320C25 has a serial port similar to the TMS370, but with additional clocking and synchronization pins.

The C25's Serial Port's circuitry contains double buffering of both the transmit and receive registers. The C25 can transmit data in either 8-bit or 16-bit blocks. There are also two modes of transmission, with or without frame synchronization pulses (FSX/FSR). These serial ports (C25) are fully static, e.g., the data contained is not lost, and to transmit/receive data CLKX/CLKR must be present.

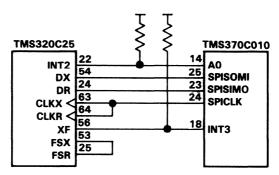

(For a complete description of the TMS320C25, see the TMS320C25 User's Guide.) An example of a typical interconnection using a TMS370C010 is shown below.

Figure 4-3. TMS370C010 - TMS320C25 Interface Example

In the setup shown below, data to and from both devices is clocked using the SPICLK. The TMS370 is configured so that receipt of an INT3 signal causes the TMS370 to load the SPIDAT register to start the SPICLK. If the TMS320C25 wants to initiate the conversation, it pulls INT3 low, waits for SPIDAT and is clocked out by the SPICLK. If the TMS370 wants to transmit. it sends out a logic 0 on A0, which is tied to INT2 on the TMS320C25. The TMS320C25 then loads the transmit buffer (DXR) to set up the synchronization circuitry(FSX/FSR). This in turn will cause the TMS320C25 to bring XF low, which activates the TMS370 INT3 routine to start the transfer. seemingly complicated handshaking is necessary because both the TMS320C25 and the TMS370 want to be in control of the transmission. The TMS320C25 needs to generate its FSX/FSR pulse before data transmission. so it has to know when a data transfer is going to happen. By using the interrupt scheme to control the transmission, a data transfer will not start until both devices are ready. The following procedures summarize the actions required when either device wants to transmit:

#### TMS320C25 wants to transmit:

C25 loads DXR

C25 toggles XF low TMS370 executes INT3 routine Places data to be transmitted in buffer.

Generates TMS370 INT3.

### TMS370 wants to transmit:

TMS370 sets SPEAK370 bit TMS370 toggles A0 low C25 loads DXR

C25 toggles XF low TMS370 executes INT3 routine C25 clears INT2 Flag TMS370 is initiating the transmission. Generates TMS320 INT2. Places data to be transmitted in buffer. Generates TMS370 INT3.

C25 did not initiate transmission.

#### TMS370 INT3 routine

If first time to transmit/receive TMS370 transmits 1 character TMS370 transmits 8 characters

If SPEAK370=0 TMS370 clears INT3 flag TMS370 clears SPEAK370 flag Cause TMS320C25 to generate synchronization pulse (FSX/FSR). TMS370 shifts out 8 characters to TMS320 TMS320 shifts out 8 characters to TMS370 TMS320C25 initiated transmission, Ready for next transmission. Default TMS320 transmitting

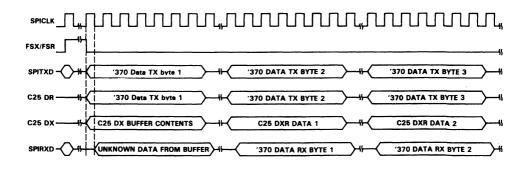

Figure 4-4 shows the timing diagram of the Continuous mode of 8-bit data transmission.

Figure 4-4. Continuous Mode No Frame Synchronization Pulse

Due to the double buffering of the transmitter, the TMS370 must also clock the C25 for one byte (word) of data to clear the buffer register, and then an-

other clocking sequence to receive the data. Therefore the C25 data is always received by the TMS370 one character after being loaded into the C25 DXR.

Different protocols can have different benefits, and which is used depends on the requirements of the system. If the system requires continual transmission of data from the C25 then the No Frame Synchronization Mode (No FSX/FSR pulse) allows greater through-put as well as less system overhead on the TMS370 processor.

If the system only has periodic data transmission of data between the two processors, and the data needs to be transmitted immediately, then the TMS370 needs to give 16 SPICLK cycles for the data from C25 to be received by the TMS370 sooner. The first byte from the C25 is dummy data. This procedure is not as efficient as the previous method, but for single bytes being transmitted between long intervals the data is transferred quicker. This is due to the TMS370 not having to wait for the C25 to load the next byte of transmit data into the buffer for transmission.

Both processors' flexible modes of transmission (such as C25's ability to transmit in either 8-bit or 16-bit mode) allows customization to the parameters of the desired system. The routines shown do not incorporate any checks if both the C25 routine and TMS370 routine try to communicate at the same time. If a situation like this occurred, both processors would think that they initiated the communication and would ignore the received data. If your system has the possibility of these asynchronous communications occurring at the same time, then a proper protocol needs to be defined.

The source code for the TMS370 in this application is as follows:

```

.title

"TMS370 - TMS320C25 Interface Continuous Mode"

This is the framework of source code for an interface between a

TMS370 microcontroller and a TMS320C25 DSP.

The external

interrupts on both devices are used to synchronize the data transfer.

Set up equate table for Peripheral File registers used in the routine.

SPICCR

.equ

P030

;SPI register assignments.

SPICTL

P031

.equ

SPIBUF

.eau

P037

SPIDAT

P039

.equ

SPIPC1

P03D

.equ

SPI-PC2

P03E

.equ

SPIPRI

.equ

PO3F

ADATA

P022

.equ

ADIR

.equ

P023

INT1

P017

.equ

INT2

.equ

P018

INT3

P019

.equ

Allocate register space for communications flags and data registers.

COM370

;Status register for TMS320-TMS370 comm.;=1 if TMS370 is transmitting;=1 C25 in continuous mode, need to

.equ

R4

0,COM370

SPEAK370 .dbit

7,COM370

FIRSTX

.dbit

; generate first sync pulse.

DATAIN

.equ

R5

; Received data.

DATAOUT

R6

.equ

;Data to be transmitted.

07000H

.text

START

DINT

;Disable all interrupts.

#100,B

MOV

;SET STACK POINTER TO R100

```

```

LDSP

Initialize SPI, APORT, and communication status flag.

MOV

#087h,SPICCR

; Reset SPI, data out on rising SPICLK,

; 8-bit characters.

MOV

#006h,SPICTL

;Master, Enable TALK, Disable SPI INT.

MOV

#002h,SPIPC1

; Enable SPICLK out.

MOV

#022h,SPIPC2

;Set SPISIMO & SPISOMI out.

; ENABLE EMULATOR SUSPEND

MOV

#020h,SPIPRI

;Reset SPI, data out on rising SPICLK,

MOV

#007h,SPICCR

; 8-bit characters. ;Set AO as output.

MOV

#001h,ADIR

;Set AO high.

MOV

#001h,ADATA

;Initialize interrupt 1

MOV

#01H,INT1

MOV

#01H,INT2

;Initialize interrupt 2

MOV

#01H,INT3

;Initialize interrupt

SBIT0

SPEAK370

;Default is TMS370 not speaking.

FIRSTX

SBIT1

;Initialized as first Transmission

MOV

#OOH, DATAOUT

;Initialize the data out register.

;Enable Interrupts

EINT

Place main program here. When TMS370 is ready to transmit, it will call subroutine TRANSMIT. This will cause an interrupt in the TMS320 which will in turn activate INT1 in the TMS370. When the TMS320 wants

;

;

When the TMS320 wants

;

to initiate a transfer it will generate an INT1 interrupt, causing the part to execute the INT1 service routine which will prepare it to

:

;

initiate a transfer. Since both transmissions by the TMS320 and

;

TMS370 involve calling the TMS370 INT1 routine, the SPEAK370 bit is set by the TMS370 when it initiates a transfer. The data to be

:

;

transmitted is stored in DATAOUT and received data, if it is valid,

will be stored in DATAIN.

:

MAIN

. . .

:

370 Initiates the data transfer to the C25, set appropriate Flags.

;

SBIT1 SPEAK370

;TMS370 is initiating transfer.

TRANSMIT

;Write 0 to AO, trigger INT1 in TMS320.

;Release TMS320 INT1.

AND

#OFEh, ADATA

OR

#001h,ADATA

RTS

;Return from subroutine (after INT1 call)

This routine is called when the

Interrupt 3 service routine.

TMS370 is going to transmit or receive data.

Do frame sync once (FIRSTX).

JBITO FIRSTX, DATA

; If NOT the first Transmission goto DATA

INTR3

SBITO FIRSTX

;Clear FLAG FIRSTX, this is first time

VOM

#080h,SPICCR

;Set Character size=1 bit

#000h,SPICCR

:Reset SPI, data out on rising SPICLK,

MOV

MOV

#000h, SPIDAT

;Transmit dummy pulse to make TMS320

;generate FSX/FSR sync pulse.

WAIT1

BTJZ

#040h, SPICTL, WAIT1

; Wait until character has been sent.

MOV

SPIBUF, DATAIN

:Clear SPI Flag

;RESET SPI, Character size=8 bit

;Enable SPI, Character size=8 bit

MOV

#087h,SPICCR

MOV

#007h,SPICCR

;Transmit data to TMS320.

If SPEAK370=0,

DATA

MOV

DATAOUT, SPIDAT

; this may be dummy data.

BTJZ

#040h, SPICTL, WAIT2

;Wait until character has been sent.

WAIT2

JBIT1 SPEAK370, DONE

;If TMS370 is talking, do not save data.;Save received data, Clear SPI Flag

MOV

SPIBUF, DATAIN

DONE

AND

#07Fh,INT3

:Clear INT1 flag.

;Clear TMS370 transmission flag.

SBITO SPEAK370

;End of INT3 routine.

RTT

;Interrupt 2 routine

INTR2

MOV

#01H, INT2

:Clear and enable interrupt 2 Flag

```

RTI

XMIT

LAC

CALL

EINT

IDLE

RET

DXR

XMTISR

```

INTR1

;Interrupt 1 routine

MOV

#01H, INT1

;Clear and enable interrupt 1 Flag

RTI

Set up interrupt vector addresses.

"Vectors", 07FF4H

.sect

;Vector goes to 'START'.;Vector goes to 'START'.

.word

START

.word

START

.word

INTR3

;INT3 vector.

.word

INTR2

;INT2 vector.

.word

INTRl

;INT1 vector.

.word

START

;Reset vector.

The source code for the TMS370C25 in this application is as follows:

sample program for interfacing the TMS370C10 and

the TMS320C25 serial ports.

; serial port receive register ; serial port transmit register

DRR:

.equ

0

DXR:

.equ

1

; interrupt mask register

IMR:

.equ

DATA:

96

.equ

; general purpose register

"AORGO"

.sect

В

START

; power-up reset

"AORG1"

.sect

В

INT2

; interrupt 2 service routine

"AORG2"

.sect

RXINT

; serial port receiver interrupt

.sect

"AORG3"

START:

.equ

$

DIÑT

; disable interrupts

; point to page 0; set serial port to 8-bit mode

0

LDPK

FORT

Offc4h

LALK

; enable interrupt 2

SACL

TMR

STXM

; FSX is output

RFSM

; continuos mode

ZAC

; zero the accumulator

SACL

DRR

; initialize receive register

SACL

DXR

; initialize transmit register

EINT

Main body of program goes here. To initiate data transfer to the TMS370 CALL subroutine XMIT. Doing this tells the 370 to start clocking, and

the 320 knowns not to save the received data. When subroutine INT2 is

entered the 320 again tells the 370 to start clocking the serial port

*

and the 320 knows that it needs to save the data it receives. RXISR

```

lets the processor know when the when data has been receive.

: data.

; enable interrupts

; load data for transmission

; initiate data transfer to 370

; wait for received data, do not save received

```

INT2:

.equ

RPŤK

40

; give 370 enough time to detect ; the XF generated interrupt. Then

NOP

CALL

XMTISR

; initiate data transfer to 370

LALK

Offd4h

; enable int2, rxint

SACL

IMR

EINT

; enable interrupts

IDLE

; wait for received data

; load accumulator with Data Receive Register. ; save only lower 8 bits

LAC

DRR

Offh

ANDK

DATA

; store received data

SACL

RET

RXISR:

$

; Serial receive interrupt

.equ

EINT

; enable interrupts

RET

XMTISR: .equ

; initiate data transfer to 370 routine.

$

; toggle XF flag low, causes 370 interrupt

RXF

NOP

NOP

NOP

SXF

; and then high, to clear. only want 370 INT3

; routine to execute once.

RET

```

# **Section 5**

# **SCI Module Description**

#### 5.1 The SCI - How It Works

The SCI module is a high-speed serial I/O port that permits Asynchronous or Isosynchronous communication between the TMS370 and other peripheral devices such as keyboards, display terminal drivers, and RS-232 interfaces. The SCI transmit and receive registers are double-buffered to prevent data collisions. In addition, the TMS370 SCI is a full duplex interface, allowing for simultaneous transmission and reception of data. Parity checking is done with on-chip hardware, eliminating the need for software overhead. The SCI is designed with the ability to do data formatting and integrity checking in hardware, further increasing execution speed.

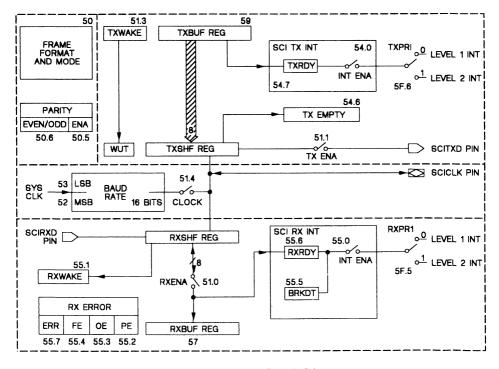

The SCI module contains 4 major blocks as shown below: an 8-bit receiver and associated interrupt hardware, an 8-bit transmitter with its interrupt hardware, a programmable clock for setting the baud rate, and frame/format/parity error circuitry.

Figure 5-1. SCI Block Diagram

### 5.2 Choosing SCI Protocols and Formats

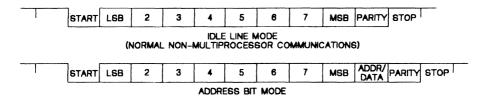

Data formatting is a characteristic of the SCI that sets it off from standard serial communications interfaces such as shift-registers. The basic unit of data is called a character and is 1 to 8 bits in length. Each character of data is formatted with a start bit, 1 or 2 stop bits, and optional parity and address bits. A character of data along with its formatting information is called a frame. Frames are organized into groups called blocks. A block of data usually begins with an address frame which specifies the destination of the data as determined by the user's protocol.

The start bit is a low bit at the beginning of each frame which marks the beginning of a frame. The SCI uses an NRZ (Non-Return-to-Zero) format, which means that in an inactive state the SCIRX and SCITX lines will be held high. Peripherals are expected to pull the SCIRX and SCITX lines to a high level when they are not receiving or transmitting on their respective lines.

The different SCI data framing formats are shown in Figure 5-2.

Figure 5-2. SCI Data Frame Formats

With the exception of the start bit and NRZ formatting, all the elements mentioned above are user programmable. These are controlled by the SCI Communication Control Register (SCICCR). The SCI Control registers are shown in Appendix B.

- 1) Protocols: The TMS370 SCI supports two protocols, the Idle Line and Address Bit modes. The two formats differ in how they distinguish the beginning of a block. The Address Bit mode adds an extra bit to each frame of transmitted data. Setting this bit to a logic 1 means that the current frame is an address. In the Idle line mode, an address frame is the first frame following an idle period of ten bits or more. The protocol is selected with the ADDRESS/IDLE WUP (SCICCR.3) bit.

- 2) Character Length: The length of the character to be transmitted is programmable from 1 to 8 bits. Data loaded into TXBUF is automatically right-justified (normal byte format) for transmission. When receiving data in RXBUF the data is also right-justified. Data are transmitted and received LSb first. If the character length is less than 8 bits the data value is automatically buffered by leading 0s. Character length is set by programming the SCI CHAR (SCICCR.0-2) bits to the values shown in Table 5-1.

| SCI<br>Char2 | SCI<br>Char1 | SCI<br>Char0 | Character<br>Length |

|--------------|--------------|--------------|---------------------|

| 0            | 0            | 0            | 1                   |

| 0            | 0            | 1            | 2                   |

| 0            | 1            | 0            | 3                   |

| 0            | 1            | 1            | 4                   |

| 1            | 0            | 0            | 5                   |

| 1            | 0            | 1            | 6                   |

| 1            | 1            | 0            | 7                   |

| 1            | 1            | 1            | 8                   |

Table 5-1. Transmitter Character Bit Length

- 3) Parity: Parity is a method of checking the integrity of a transmitted/received character. It sends an extra bit with the character to make sure that the sum of 1s in the character is an odd or even number. Parity checking and generation is done on-chip in hardware. It may be enabled or disabled, and if used it can be set odd or even. Bits 5 and 6 of the SCICCR register control the parity checking.

- 4) Stop bits: A stop bit is a high bit of data transmitted at the end of a frame. The number of stop bits can be one or two, depending on your application. In general, data integrity is more secure if two bits are used because the SCI is more likely to catch a framing (SCI synchronization) error. Adding the extra bit increases the number of bits transmitted per character, however, and slows the throughput of the serial port.

#### 5.3 The SCI SW RESET Bit

The SCI SW RESET Bit (SCICTL.5) is used to reset the condition of the SCI state machine and operating flags. Writing a 0 to this bit sets the operating flags to their reset state and halts the operation of the SCI. This must be done before using the SCI for the first time or after a system RESET to guarantee the state of the SCI. Writing a 1 to the bit releases the SCI state machine and allows the SCI to resume operation.

It is good practice to reset the SCI by writing a 0 to the SCI SW RESET bit before setting up the control registers. The registers are then set to the desired value and a 1 is written to the SCI SW RESET Bit to release the SCI. This stops the operation of the SCI while it is being configured initially. The SCICTL control register values can be set in the same instruction that sets the SCI SW RESET bit to 1.

### 5.4 Operating Modes of the SCI

The SCI has two modes of operation. The first, Asynchronous, is the most commonly used mode and requires no synchronizing clock between the TMS370 and a peripheral device. When transmitting in the Asynchronous mode, each bit is held for 16 shift-clock cycles. This repetition insures that the data will be present long enough for the unsynchronized receiver to get valid data.

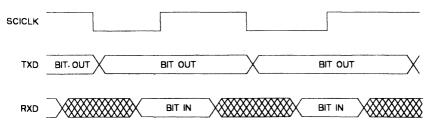

In the Isosynchronous mode, a common clock is used to increase system throughput by synchronizing the data transfer between the TMS370 and another serial port. In this mode, one bit of the frame is shifted out on every shift-clock cycle. Using the Isosynchronous mode gives a data transfer rate 16 times the corresponding Asynchronous SCICLK rate, but requires an extra line to carry the SCICLK signal. The Isosynchronous mode is superior to simpler synchronous communications such as the SPI in that you can achieve near synchronous communication speeds but still use formatting to assure data integrity. The format for Asynchronous and Isosynchronous communications is shown in Figures 5-3 and 5-4.

Figure 5-3. Asynchronous Communication Format

Figure 5-4. Isosynchronous Communication Format

### 5.5 Setting the SCICLK Pins and Baud Rate

The SCICLK is usually configured internally for Asynchronous communications, but can be external if your application requires it. For Isosynchronous communications the clock can be configured internally or externally depending on whether the TMS370 will be issuing the clock signal. If the SCICLK pin is not configured as the serial clock(SCICLK FUNCTION=0), then the pin may be used for general purpose I/O by setting SCICLK DATA DIR(SCIPC1.0) to the appropriate value and reading or writing to SCICLK DATA IN or DATA OUT. When the SCICLK is enabled (SCICLK FUNCTION=1), the contents of SCICLK DATA DIR, DATA IN, and DATA OUT are ignored.

Even though the clock is configured internally and is "independent" in the Asynchronous mode, it is necessary to have the baud rates set to exactly the same value in the transmitting and receiving devices so that the receivers can synchronize correctly on the frames. This holds whether communications are between two TMS370's or a TMS370 and a different peripheral device. The baud rate is set by writing a 16-bit value to the Baud Rate Select registers, BAUDMSB and BAUDLSB. The equations used to calculate the baud rate register values are shown below:

```

Asynchronous Baud Rate = CLKIN / [ (BAUD RATE REG + 1) x 128 ]

Isosynchronous Baud Rate = CLKIN / [ (BAUD RATE REG + 1) x 8 ]

```

Table 5-2 gives the Baud Rate Register values for common Asynchronous baud rates and frequencies. The values for Isosynchronous baud rates can be similarly calculated.

Table 5-2. Asynchronous Baud Rate Register Values for Common SCI Baud Rates

|           | Crystal Oscillator Frequency (MHz) |      |        |      |         |      |        |       |

|-----------|------------------------------------|------|--------|------|---------|------|--------|-------|

|           | 2.4576                             |      | 7.3728 |      | 19.6608 |      | 20.00  |       |

| Baud Rate | BR Reg                             | %ERR | BR Reg | %ERR | BR Reg  | %ERR | BR Reg | %ERR  |

| 75        | 255                                | 0.00 | 767    | 0.00 | 2047    | 0.00 | 2082   | 0.02  |

| 300       | 63                                 | 0.00 | 191    | 0.00 | 511     | 0.00 | 520    | -0.03 |

| 600       | 31                                 | 0.00 | 95     | 0.00 | 255     | 0.00 | 259    | 0.16  |

| 1200      | 15                                 | 0.00 | 47     | 0.00 | 127     | 0.00 | 129    | 0.16  |

| 2400      | 7                                  | 0.00 | 23     | 0.00 | 63      | 0.00 | 64     | 0.16  |

| 4800      | 3                                  | 0.00 | 11     | 0.00 | 31      | 0.00 | 32     | -1.38 |

| 9600      | 1                                  | 0.00 | 5      | 0.00 | 15      | 0.00 | 15     | 1.73  |

| 19200     | 0                                  | 0.00 | 2      | 0.00 | 7       | 0.00 | 7      | 1.73  |

| 38400     | -                                  | -    | -      | -    | 3       | 0.00 | 3      | 1.73  |

| 156000    | -                                  | -    |        | -    | -       | -    | 0      | 0.16  |

BR Reg = 16 bit Baud rate register value

Note: When using an externally generated SCICLK in Isosynchronous mode, the maximum speed at which the SCICLK can run is limited to CLKIN/40. This is necessary so that the internal clocks of the SCI have time to synchronize with the external clock. For this reason it is recommended to use the TMS370 to drive the master serial clock in a system where maximum throughput is a major concern.

# 5.6 SCI Receiver Operation

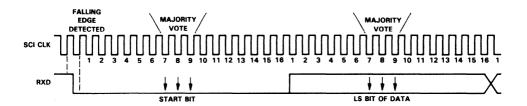

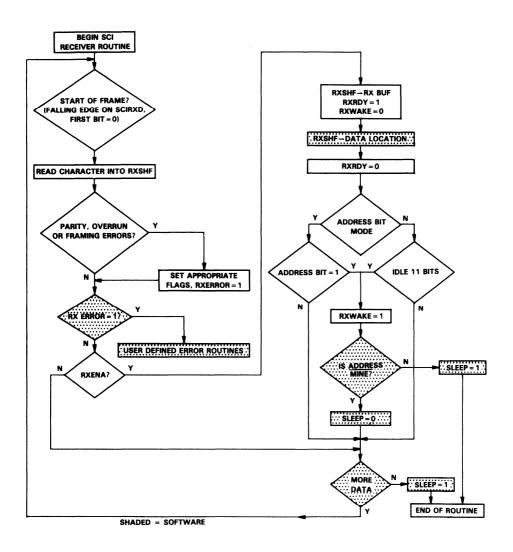

A flowchart showing the operation of the receiver is shown in Figure 5-5. When the SCI senses a falling edge on SCIRXD the flow described below begins. Depending on the protocol and format, the receiver checks for transmission errors and loads the data into RXSHF, the receiver shift register. When the number of bits specified by the SCI character length control bits have been read in, the contents of RXSHF are transferred to the receiver data buffer, RXBUF, and the RXRDY flag is set to show that the data value is ready to be read. An SCI receiver interrupt is generated if the SCI receiver interrupt is enabled.

If errors were detected, the RXERROR and specific error(Parity, Framing, Overrun, Break) flags are set by the hardware and operation continues. Error control is done in software. If multiprocessor communications are being used, frames received are checked to see if they are address frames and the appropriate bits are set.

Figure 5-5. Receiver Operation Flowchart

- 0

### 5.7 SCI Transmitter Operation

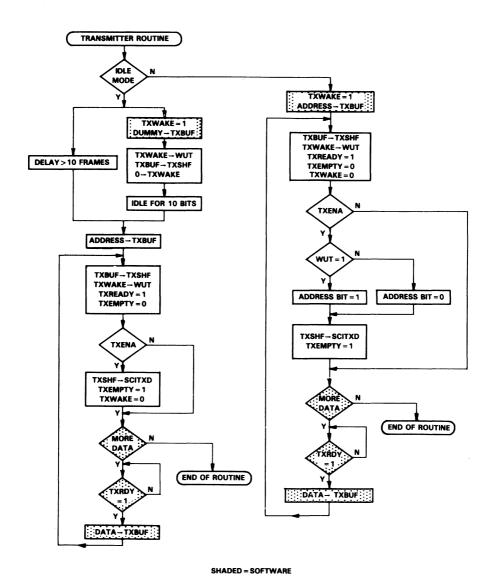

A flowchart of the operation of the SCI transmitter is shown in Figure 5-6. The SCI transmitter is activated by loading the transmitter buffer, TXBUF, which clears the TXRDY flag. When TXSHF, the transmitter shift register, is empty, the contents of TXBUF are latched into TXSHF and the TXRDY flag is set to indicate the transmitter is ready for a new character. Depending on the protocol and format, the transmitter formats the data as needed to signal the beginning and end of frames of data.

Figure 5-6. Transmitter Operation Flowchart

Data transmission is initiated by moving data into TXBUF. The status of the TXWAKE flag, set prior to writing to TXBUF, determines whether or not the current character is an address or data. The contents of TXWAKE and TXBUF are transferred to WUT(Wake Up Temporary) and TXSHF, respectively, to be shifted out as soon as the current transmission is complete. WUT and TXSHF are the actual transmission buffers and cannot be written to directly, only through TXWAKE and TXBUF. This double buffering of the transmission registers allows you to begin setting up for the transmission of a new character before the previous character has been shifted out of TXSHF, speeding up data transfer. Data is shifted out of TXSHF LSb first.

It should be noted that there are two ways to initiate a block signal when using the Idle Line protocol. The first is to write a 1 to the TXWAKE bit and then write dummy data to the TXBUF register. The transmitter will idle for 10 bits, signalling a block start. The other method is to simply wait for a period of time greater than the transmitter takes to transmit 10 bits (this is determined from the SCICLK frequency) and write the address to TXBUF.

#### 5.8 SCI Interrupts and Flags

The SCI interrupt logic generates interrupt flags when it receives or transmits a complete character as determined by the SCI character length. This provides a convenient and efficient way of timing and controlling the operation of the SCI transmitter and receiver. The interrupt flags for the transmitter and receiver are TXRDY (TXCTL.7) and RXRDY (RXCTL.7), respectively. The TXRDY flag is set when a character is transferred to TXSHF and TXBUF is ready to receive a new character. In addition, when both the TXBUF and TXSHF registers are empty, the TX EMPTY flag (TXCTL.6) is set. The TXRDY flag signals that you can write another character to TXBUF, and the TX EMPTY flag is set when no new data value has been written to TXBUF and the SCI has finished transmitting.

When a new character has been received and shifted into RXBUF, the RXRDY flag is set. The status of data transfers can be checked by polling the flags. In this way the risk of a receiver overrun or transmitter corruption can be avoided.

The interrupts associated with the receiver and transmitter can be enabled or disabled using the SCI RX INT ENA (RXCTL.0) and SCI TX INT ENA (TXTCL.0) bits, respectively. When the interrupts are enabled and the flag is set, that particular interrupt is asserted. The priority of the SCI RX and TX interrupts can be set independently using the SCI TX and RX priority bits (SCI-PRI.5-6). Note that unless the RXENA bit (SCICTL.0) is set, the received data will not be shifted into RXBUF and no interrupt will be generated. Data loaded into TXBUF will not be shifted out unless the TXENA bit is set.

### 5.9 Multiprocessor Communications

#### 5.9.1 Using the SLEEP Bit

Quite often several serial ports will be tied to a common line, and a method is needed to restrict the conversation between two devices to avoid a communications conflict. The SLEEP flag can be used to disable an SCI until the start of a new block, at which time an address check can be made to see if that particular receiver is being addressed. The SLEEP bit is used in both Idle and Address Bit modes.

For the single microcontroller system SLEEP is initialized to 0. In a multiprocessor environment the SCI uses the SLEEP (SCICTL.2) flag to control when a specific receiver is addressed. In a multiprocessor system the SLEEP flag is initialized to a 1. Until a Sleeping receiver receives block start signal, the following happens:

- 1) SCIRX continues to load RXSHF

- 2) No format errors are recognized(OE=FE=PE=0), but BRKDT still is.

- 3) Data is shifted into RXBUF, but RXRDY is not set.

- 4) RXINT is disabled.

A block start signal acts like an alarm clock for the sleeping SCI receiver. A block start signal signifies that the current is an address. In the Address Bit mode, this is signalled by Address Bit=1. In the Idle mode, a block starts when a low bit is detected after an idle period of 10 bits or more. When a block start signal is received, the data received (an address) is loaded normally, including the RXWAKE flag. At this point the receiver interrupt will be called if enabled and the address byte received is checked, in software, against the "key" for that particular processor. If it matches, the software needs to clear the SLEEP bit and return to the main loop to read the rest of the block; if not, put the part back to bed (SLEEP=1), return to the program and wait until another block start is detected. Clearing the SLEEP bit informs the microcontroller that the following frames are data and not addresses.

#### 5.9.2 Using the TXWAKE Bit

The TXWAKE bit is used by the transmitter to format the data going out as an address frame or a data frame. If a data character is being transmitted, the TXWAKE flag is left 0. If an address needs to be sent, TXWAKE is set to 1 before the address byte is loaded into TXBUF. The TXWAKE flag is automatically cleared when the byte is shifted from TXBUF to TXSHF.

Depending on which protocol you are using (Address Bit or Idle) setting the TXWAKE bit has different effects. If the Address Bit mode is being used, the Address bit will be set for that frame as it is transmitted out. If the Idle bit mode is being used, the transmitter goes idle (transmits a logic high) for a period of 10 bits when TXBUF is loaded. This is in effect a dummy write; the next data written to TXBUF will be the address and will be transmitted out as the address frame. Depending on your application, it may not be necessary to use the TXWAKE bit. If your design has only one peripheral or device tied to the SCI, then address bytes are not needed. TXWAKE can be left 0 for the duration of the transmission and no address bits will be sent.

#### 5.9.3 Disabling the SCI Transmitter

Because the SCI uses the NRZ format, the transmitter is actually outputting a logic 1 when data is not being transmitted. If the SCITXD line is going to be tied to a bus it will be necessary to put the line in a three-state condition so that the line is not constantly being driven high. This is done by reconfiguring the SCITX pin as general I/O after transmission. Setting the SCI TXD FUNCTION bit = 0 and the SCI TXD DATA DIR = 0 will put the pin into an input configuration that will prevent bus conflicts from occurring.

# 5.9.4 Choosing the Right Protocol